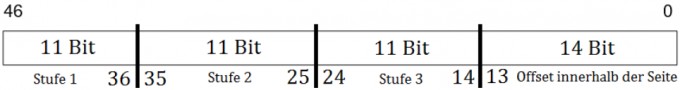

Die Page Size ist (16\)KB, d.h. \(14\) Bits Page Offset. Bei einer \(47\) Bit langen virtuellen Adresse bleiben \(47-14 = 33\) Bits für die einzelnen Page Tables auf jeder Stufe übrig. D.h. insgesamt \(3\) mal \(11\) zur Adressierung der nächsten Stufe, da \(3\)-Level-Paging genutzt wird. Die virtuelle Adresse lässt sich in folgende Teilbereiche unterteilen:

Die Stufenzählung beginnt links:

Stufe \(1\) beschreibt ist die äußere Page Table mit \(2^{11}\) Einträgen.

Stufe \(2\) beschreibt die erste innere Page Table mit \(2^{11}\) Tabellen mit jeweils \(2^{11}\) Einträgen.

Stufe \(3\) beschreibt die zweite innere Page Table mit \(2^{22}\) Tabellen mit jeweils \(2^{11}\) Einträgen.

Die \(14\) Bits am Ende beschreiben den Offset innerhalb einer Seite.